Department of Computer Science Technical Report

Synthesis of State Space Generators for Model Checking Microcontroller Code

Dominique Marcel Gückel

ISSN 0935–3232 · Aachener Informatik-Berichte · AIB-2014-15

RWTH Aachen · Department of Computer Science · November 2014

The publications of the Department of Computer Science of RWTH Aachen University are in general accessible through the World Wide Web.

http://aib.informatik.rwth-aachen.de/

# Synthesis of State Space Generators for Model Checking Microcontroller Code

Von der Fakultät für Mathematik, Informatik und Naturwissenschaften der RWTH Aachen University zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften genehmigte Dissertation

vorgelegt von

# Diplom-Informatiker Dominique Marcel Gückel

$\label{eq:Greven} \begin{array}{c} \text{aus} \\ \text{Greven} \ / \ \text{Nordrhein-Westfalen} \end{array}$

Berichter: Universitätsprofessor Dr.-Ing. Stefan Kowalewski Universitätsprofessor Dr. rer. nat. Rainer Leupers

Tag der mündlichen Prüfung: 15. Oktober 2014

Diese Dissertation ist auf den Internetseiten der Hochschulbibliothek online verfügbar.

Dominique Marcel Gückel Lehrstuhl Informatik 11 gueckel@embedded.rwth-aachen.de

Aachener Informatik Bericht AIB-2014-15

Herausgeber: Fachgruppe Informatik RWTH Aachen University Ahornstr. 55 52074 Aachen GERMANY

ISSN 0935-3232

# Abstract

Creating software for embedded systems requires rigid quality measures. The reason for this is that errors in the software may have very expensive or even disastrous consequences. This gives rise to the use of formal methods for software verification, such as model checking, theorem proving, and static analysis.

Many embedded systems rely on either application-specific circuits, reconfigurable logics, or microcontrollers. Manufacturers of microcontrollers typically offer a wide variety of devices based on the same core architecture, which are equipped differently and thus offer different functionality. Furthermore, some tool chains exist that allow developers not only to choose from such off-the-shelf devices, but to customize them for specific kinds of tasks. In some cases, this may go to the extent of actually designing new architectures.

It is precisely this wide variety of available devices that complicates the use of automated verification. Tools need to be adapted to a new platform, or even recreated in case they should be implemented in a too hardware-dependent way.

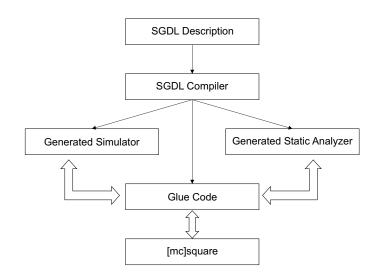

The topic this thesis deals with is the reduction of the necessary effort for adapting a verification tool to new microcontrollers. To this end, we designed a language for describing microcontrollers, SGDL, and a compiler for translating such descriptions into operative simulators and static analyzers. We based our work on [MC]SQUARE, which is a platform for model checking and static analysis of assembly code software.

In order to counter the state explosion problem, it is also necessary to include abstractions in generated simulators. We illustrate, on a number of abstraction techniques, how they can be integrated into the approach and whether they can be generated either partly or entirely.

A number of case studies concerning the implementation of simulators with our new language is presented. Additionally, we examine the effectiveness of the aforementioned abstractions that are integrated into the generated simulators, and compare the results to those obtained when using manually implemented simulators.

# Zusammenfassung

Die Implementierung von Software für eingebettete Systeme erfordert strenge Maßnahmen zur Qualitätssicherung. Der Grund hierfür ist, daß Fehler in dieser Art von Software sehr teuer werden oder gar katastrophale Auswirkungen haben können. Hieraus motiviert sich der Einsatz formaler Methoden zur Verifikation von Software, wie etwa Model-Checking, Theorem Proving, oder statischer Analysen.

Viele eingebettete Systeme basieren entweder auf applikationsspezifischen Schaltungen, rekonfigurierbarer Logik, oder Mikrocontrollern. Typischerweise bieten die Hersteller von Mikrocontrollern eine Vielzahl verschiedener Geräte mit der gleichen Kernarchitektur an, die sich im Hinblick auf die verfügbare Ausstattung unterscheiden. Darüber hinaus gibt es Software-Werkzeuge, mit denen Entwickler bestehende Mikrocontroller an ihre eigenen Anforderungen anpassen oder sogar bei Bedarf neue Architekturen entwickeln können.

Aus der Vielfalt an verfügbaren Geräten ergeben sich allerdings auch Nachteile. Die Möglichkeit zur automatisierten formalen Verifikation wird eingeschränkt, weil die dafür benötigten Werkzeuge zunächst einmal an jede neue Plattform angepaßt werden müssen. Je nach Werkzeug kann dies auch bedeuten, daß eine komplette Neuimplementierung nötig wird.

Das Thema dieser Dissertation ist die Reduktion des Aufwandes, der nötig ist, um ein Verifikationswerkzeug an neue Mikrocontroller anzupassen. Zu diesem Zweck haben wir eine Sprache zur Beschreibung von Mikrocontrollern entworfen, SGDL, und einen Compiler implementiert, der Beschreibungen in dieser Sprache übersetzen kann in funktionsfähige Simulatoren und statische Analyse-Werkzeuge. Unsere Arbeit basiert auf [MC]SQUARE, einer Plattform für das Model-Checking und die statische Analyse von Assembler-Code.

Um das Problem der Zustandsexplosion zu begrenzen, ist es erforderlich, daß die generierten Simulatoren auch Abstraktionstechniken unterstützen. Anhand einer Reihe von Abstraktionstechniken zeigen wir, wie diese in den vorgestellten Ansatz integriert werden können, und inwieweit es möglich ist, sie ganz oder teilweise automatisch zu erzeugen.

In unseren Fallstudien demonstrieren wir die Implementierung von Simulatoren mit unserer neuen Sprache. Darüber hinaus untersuchen wir die Wirksamkeit der bereits genannten Abstraktionstechniken in den generierten Simulatoren, und vergleichen die Ergebnisse mit denen von handgeschriebenen Simulatoren.

# Acknowledgments

First of all, I would like to thank Prof. Dr.-Ing. Stefan Kowalewski for supervising my thesis. The time I spent at his institute, the Embedded Software Laboratory of RWTH Aachen University, has been extremely helpful, and provided me with a lot of insights into several topics. I would also like to thank Prof. Dr. rer. nat. Rainer Leupers for being the second supervisor of my thesis. Furthermore, my thanks go to Prof. Dr. Ir. Joost-Pieter Katoen and Prof. Dr. Horst Lichter for being part of the examination board.

Thanks to Dr. Bastian Schlich, who introduced me into research, and encouraged me to start out as a doctoral student in the first place. Also thanks to the other researchers in the [MC]SQUARE project, namely Dr. Jörg Brauer, Sebastian Biallas, and Volker Kamin.

Thanks also to my former colleagues at the Embedded Software Lab, who have made my time there both interesting and delightful. Special thanks go to Dr. Andre Stollenwerk.

I am especially grateful for the assistance provided by Ben Titzer and Jens Palsberg in the early days of my research project.

Originally, I started my research as a scholarship holder in the DFG Research Training Group 1298 *AlgoSyn*, which funded me for the first three years at the Embedded Software Laboratory. The environment provided by AlgoSyn, i.e., the tutorials, mini lectures, and regular presentations, was really beneficial for my research. Most of all, I am extraordinarily grateful that AlgoSyn funded most of the student researchers who assisted me in my work.

This research would not have been possible without the contribution of several students. First and foremost, my thanks go to Ivica Bogosavljevic. Furthermore, I would like to thank Florian Caron, Christian Dehnert, Richard Musiol, Irfan Simsek, Norbert Wiechowski, and all other team members who have contributed directly or indirectly.

Thanks also to my superiors at IVU Traffic Technologies for granting me the vacation required for preparing the oral exam. I really appreciate this, as the request was granted on very short notice.

Finally, I would like to thank my family and my friends for their support of all kind during the long years of research!

Aachen, November 2014

# Contents

| 1 | Intro | oduction 1                                        |  |  |  |  |  |  |  |  |  |  |  |

|---|-------|---------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|   | 1.1   | Objectives                                        |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.2   | Contribution                                      |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.3   | Outline                                           |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.4   | Bibliographic Notes                               |  |  |  |  |  |  |  |  |  |  |  |

| 2 | Prel  | iminaries 5                                       |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.1   | Notations                                         |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.1.1 Number Representations                      |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.1.2 Fonts                                       |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.2   | Kripke Structures                                 |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.3   | Temporal Logics                                   |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.3.1 LTL                                         |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.3.2 CTL                                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.4   | Model Checking                                    |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.4.1 Specification                               |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.4.2 Modeling                                    |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.4.3 Verification                                |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.5   | Static Analysis                                   |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.5.1 Motivation                                  |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.5.2 Control Flow Analysis                       |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 2.5.3 Data Flow Analysis 15                       |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.6   | [MC]SQUARE                                        |  |  |  |  |  |  |  |  |  |  |  |

| 3 | Har   | dware Descriptions 21                             |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.1   | Reasons for Describing Hardware                   |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.1.1 Tool Retargeting                            |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.1.2 Synthesis and Simulation of Actual Hardware |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.1.3 Design Space Exploration                    |  |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.1.4 Verification of Hardware                    |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.2   | 2 Survey of Existing Approaches                   |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.3   | Requirements Analysis                             |  |  |  |  |  |  |  |  |  |  |  |

| 4 | A Sy |                       | for Synthesizing Simulators              | 29 |  |  |  |  |  |  |  |  |  |  |

|---|------|-----------------------|------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|

|   | 4.1  |                       | res                                      | 29 |  |  |  |  |  |  |  |  |  |  |

|   | 4.2  |                       | tecture                                  | 30 |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.2.1                 | Description of Input                     | 30 |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.2.2                 | Processing the Input                     | 32 |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.2.3                 | Generated State Space Generators         | 33 |  |  |  |  |  |  |  |  |  |  |

|   | 4.3  |                       | Space Building                           | 33 |  |  |  |  |  |  |  |  |  |  |

|   | 4.4  |                       | Analyzers                                | 33 |  |  |  |  |  |  |  |  |  |  |

|   | 4.5  | Abstra                | action                                   | 34 |  |  |  |  |  |  |  |  |  |  |

| 5 | Stat | -                     | e Generator Description Language         | 35 |  |  |  |  |  |  |  |  |  |  |

|   | 5.1  | Overv                 | riew                                     | 35 |  |  |  |  |  |  |  |  |  |  |

|   | 5.2  | Memo                  | ory Description                          | 36 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.2.1                 | Memory Declaration                       | 37 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.2.2                 | Memory Alias Declaration                 | 38 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.2.3                 | Memory Initialization                    | 40 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.2.4                 | Mandatory Memories                       | 41 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.2.5                 | Memory Cell Dependencies                 | 42 |  |  |  |  |  |  |  |  |  |  |

|   | 5.3  | Instru                | ction Set Description                    | 43 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.3.1                 | Encoding Format Declarations             | 43 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.3.2                 | Operand Type Declarations                | 44 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.3.3                 | Instruction Element                      | 45 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.3.4                 | Global Attribute "instruction word size" | 52 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.3.5                 | Subroutine Declarations                  | 52 |  |  |  |  |  |  |  |  |  |  |

|   | 5.4  | Atomics               |                                          |    |  |  |  |  |  |  |  |  |  |  |

|   | 5.5  | Loade                 | r Description                            | 54 |  |  |  |  |  |  |  |  |  |  |

|   | 5.6  | Mode                  | ling of Peripherals                      | 55 |  |  |  |  |  |  |  |  |  |  |

|   | 5.7  | Mode                  | ling of Interrupts                       | 56 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.7.1                 | Interrupt Vector Table                   | 57 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.7.2                 | Operational Behavior of Interrupts       | 58 |  |  |  |  |  |  |  |  |  |  |

|   | 5.8  | Data '                | Types and Type System                    | 59 |  |  |  |  |  |  |  |  |  |  |

|   | 5.9  | $\operatorname{Code}$ | Blocks                                   | 59 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.9.1                 | Accessing Global Variables               | 60 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.9.2                 | Assign Statements                        | 60 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.9.3                 | Control Structures                       | 62 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.9.4                 | Local Variables                          | 63 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.9.5                 | Function Calls                           | 64 |  |  |  |  |  |  |  |  |  |  |

|   |      | 5.9.6                 | Accessing the [MC]SQUARE options         | 64 |  |  |  |  |  |  |  |  |  |  |

|   | 5.10 | Comm                  | nents                                    | 65 |  |  |  |  |  |  |  |  |  |  |

|   | 5.11 | Const                 | ants                                     | 65 |  |  |  |  |  |  |  |  |  |  |

|   |                            | Preprocessor Directives655.12.1 Defines665.12.2 Generation of Empty Source Files665.12.3 Instruction Templates665.12.4 Alias Templates665.12.5 Interrupt Template67Compilation Units67 |  |  |  |  |  |  |  |  |  |  |  |

|---|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| 6 | SGD                        | L Compiler 69                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.1                        | Outline                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.2                        | Preprocessor                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.3                        | Parser                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.4                        | Abstract Syntax Tree and Intermediate Representation                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.5                        | Static Analyzer                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |  |

|   |                            | 6.5.1 Mode of Operation $\ldots \ldots .73$                                                                      |  |  |  |  |  |  |  |  |  |  |  |

|   |                            | 6.5.2 Structure of the Analyzer                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |  |

|   |                            | 6.5.3 Instruction Set Classification                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |  |

|   |                            | 6.5.4 Further Uses                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.6                        | Compiler Backend For Code Synthesis                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.7                        | Glue Code Subcompiler                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.8                        | Related Work                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |  |

|   |                            | $6.8.1  \text{Compiler Technology} \dots \dots$                                  |  |  |  |  |  |  |  |  |  |  |  |

|   |                            | 6.8.2 Static Analysis                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |  |

| 7 | Gen                        | erated Simulators 91                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |  |

|   | 7.1                        | Resource Model                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 7.2                        | Instructions                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |  |

|   | 7.3                        | Interrupts                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |  |

|   | 7.4                        | Determinizer and Splitter                                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |

|   |                            | 7.4.1 Mode of Operation                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

|   | 7.5                        | Loaders                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

|   | 7.6                        | Disassembler                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |  |

|   | 7.7                        | Data Types                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |  |

|   | 7.8                        | Observer Interface                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

|   | 7.9                        | Validation                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |  |

| 8 | Abstraction Techniques 105 |                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |  |

| U | 8.1                        | Motivation                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |  |

|   | 8.2                        | Language Elements Related to Abstraction                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

|   | 8.3                        | Lazy Stack Evaluation                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |  |

|    | 8.4  | On-the-Fly Path Reduction                                       |

|----|------|-----------------------------------------------------------------|

|    |      | 8.4.1 Concept of and Approaches to Path Reduction               |

|    |      | 8.4.2 Condition Checking in On-the-Fly Path Reduction 112       |

|    | 8.5  | Dead Variable Reduction                                         |

|    |      | 8.5.1 Static Analysis                                           |

|    |      | 8.5.2 Generating the Static Analyzer                            |

|    |      | 8.5.3 Application in State Space Building                       |

|    | 8.6  | Delayed Nondeterminism                                          |

|    |      | 8.6.1 Concept of Delayed Nondeterminism                         |

|    |      | 8.6.2 Delayed Nondeterminism in Generated Simulators 120        |

|    | 8.7  | Sanity Check-Based Approaches                                   |

|    |      | 8.7.1 Implicit Determinization Guards                           |

|    |      | 8.7.2 Restriction to Ternary-Valued Logics                      |

|    | 8.8  | Related Work                                                    |

|    |      | 8.8.1 General Approaches Towards Countering the State Explosion |

|    |      | Problem                                                         |

|    |      | 8.8.2 Specific Approaches                                       |

| 9  | Impl | ementing Simulators With SGDL 129                               |

| 9  | 9.1  | Atmel ATmega16                                                  |

|    | 9.1  | 9.1.1 Background                                                |

|    |      | 9.1.2 Implementation                                            |

|    |      | 9.1.3 Validation                                                |

|    | 9.2  | Atmel ATmega644                                                 |

|    | 0.2  | 9.2.1 Background                                                |

|    |      | 9.2.2 Implementation                                            |

|    |      | 9.2.3 Validation                                                |

|    | 9.3  | Intel MCS-51                                                    |

|    |      | 9.3.1 Background                                                |

|    |      | 9.3.2 Implementation                                            |

|    |      | 9.3.3 Validation                                                |

|    |      |                                                                 |

| 10 |      | e Studies 143                                                   |

|    | 10.1 | Atmel ATmega16 Case Studies                                     |

|    |      | 10.1.1 Impact of Abstractions                                   |

|    | 10.0 | 10.1.2 Case Study: Window Lift                                  |

|    | 10.2 | Atmel ATmega644 Case Studies                                    |

|    |      | 10.2.1 HnPOS in [MC]SQUARE                                      |

|    |      | 10.2.2 Simple Operating System in [MC]SQUARE                    |

|    | 10.3 | Intel MCS-51 Case Studies                                       |

|    |      | 10.3.1 Setup                                                    |

|    | 10.3.2      | Verificatio | n | <br> | <br> |  | <br>• | • |  | • | • |  | 159 |

|----|-------------|-------------|---|------|------|--|-------|---|--|---|---|--|-----|

| 11 | Conclusion  |             |   |      |      |  |       |   |  |   |   |  | 161 |

|    | 11.1 Conclu | sion        |   | <br> | <br> |  |       | • |  |   |   |  | 161 |

|    | 11.2 Future | Work        |   | <br> | <br> |  |       | • |  |   |   |  | 163 |

# **1** Introduction

Nowadays, we are surrounded by countless computer systems. These systems are not necessarily immediately recognizable as such because they are integrated into other systems, and therefore, are called *embedded systems*. People normally do not interact directly with the computer system, but with the *embedding system*. In many cases, the functionality of the embedding system would not be possible without the embedded system. Typical tasks for these devices are to measure data from sensors interfacing to their environment, and respond to such input by controlling actuators that are part of the embedding system.

A very common field of application for embedded systems are cars. Several assistance systems, like anti-lock braking systems, electronic stability programs, or cruise control, are realized by means of embedded systems. In this setting, the car is the overall embedding system, which has several embedded systems integrated into it. For such tasks, it is also necessary for embedded systems to be networked, as for instance the data acquired by the systems that measure the speed of individual wheels need to be joined. Hence, even though embedded systems are typically integrated into components, they are not necessarily isolated from each other.

Another scenario for applying embedded systems are industrial plants. In such settings, the embedded systems are tasked, for instance, with controlling conveyor belts, robotic arms, and other devices necessary for production. It is also possible to control entire production processes at the field level.

There are several categories for distinguishing embedded systems. The aforementioned use of embedded systems in cars is typically referred to as an example of *product automation*, whereas their usage in plants is called *production automation*. Product automation implies that the embedded system, or systems, must not exceed given cost thresholds, as they have to be produced in quantities. Opposed to this, production plants are not built nearly as many times as products, therefore the cost for individual embedded systems is not as important. Due to this difference, the type of systems used in these settings differ. For products, frequently used devices include microcontrollers, and several types of programmable logic, e.g. Field Programmable Gate Arrays (FPGAs). Plants, on the contrary, typically rely on more elaborate and expensive devices, such as Programmable Logic Controllers (PLCs), which already provide some critical functionality required in their respective fields of application. For instance, PLCs are able to guarantee the completion of operations within a certain time, i.e., are capable of real time computations.

#### 1 Introduction

Creating similar functionality on microcontrollers is typically also possible, but requires additional effort, including the effort for establishing the correctness of such capabilities.

The correct operation of products containing embedded systems depends heavily on the correctness of the hardware and software of which the embedded system consists. Furthermore, errors in the software of such systems are particularly acute because it is virtually impossible for the vendor to apply a patch. Unlike in generalpurpose computing, the systems are typically not accessible to the end user, and in safety-critical systems like cars, it is not even desirable to expose an interface to the user. Hence, to fix mistakes, it is necessary to recall such devices, or even to replace them. Thus, it is vital for a software developer to detect errors before the system is shipped to the customer, and, to this end, apply rigid verification techniques.

## 1.1 Objectives

Embedded systems used in products are often based on processor-based architectures. In many cases, these processors are stand-alone computers on a single chip, so called systems-on-chip (SoC). This means that they are equipped with some on-chip memory, peripherals, and I/O ports for interfacing to the outside world. Microcontrollers fall into this category of devices.

Developers wanting to create a system based on microcontrollers have a wide range of devices at their disposal. Many device manufacturers sell microcontrollers, e.g. Intel, Renesas, Infineon, PIC, and Atmel. Each of these provides one or more families of controllers, and within these families, very different devices, ranging from cheap, sparsely equipped chips to complex devices with many on-chip peripherals. The latter sometimes eliminate the need for integrating further chips into a design, for instance when a microcontroller provides communication controllers for busses such as CAN. In some cases, developers can even rely on tools to create customized microcontrollers, which allows them to remove unnecessary parts and add needed ones, thus reducing the overall cost for a design.

While this wide range of devices certainly has advantages, it complicates the development of reliable software. As long as developers build their system from off-the-shelf devices from the existing manufacturers, they can typically use the development tools provided by the respective device manufacturer. In most cases, this includes assemblers, linkers, and C compilers. Developing software in C provides at least a certain degree of hardware abstraction, thus easing the porting of software in case a chosen platform should prove to be no longer suitable. However, when creating customized hardware, there is no compiler support yet. The compiler needs to be created. Software quality ensurance faces a similar problem, as existing tools also need to be rewritten or retargeted to the new platform.

Some tool chains exist that facilitate the creation of compilers, assemblers, and similar tools, for new platforms. To the best of our knowledge, however, this has so far not been the case with regard to model checkers, which are a special kind of tool for detecting errors. It is therefore our goal to create a means for doing so, such that it becomes possible to retarget a model checking tool to new platforms with time efforts that would make the procedure feasible for industrial applications.

## 1.2 Contribution

In this thesis, we make the following contributions:

- We describe a system for generating state space generators from a hardware description. The description can be created by developers in a language, SGDL, which we designed with the goal of accelerating the development of such generators.

- To illustrate the advantage of creating state space generators with our tool, instead of implementing them manually in Java, we present three implementation-related case studies. In these case studies, we used our tool chain to create simulators for the Atmel ATmega16 and ATmega644 microcontrollers and for the 8051, a member of the Intel MCS-51 family of microcontrollers.

- We show that even when synthesizing simulators instead of manually finetuning them, it is possible to integrate abstraction techniques. In this respect, we also prove that certain abstractions can be added automatically, without the developer having to be familiar at all with the concept.

- In a series of case studies consisting of executable programs for all three platforms, we compare several qualities of synthetic simulators with those of existing handcrafted simulators, some of which have been optimized over years. Our main result from these case studies is that synthetic simulators can compete with handcrafted code in most aspects.

- Finally, we develop ideas on how to further improve the generation of automatic abstractions. With this purpose in mind, we have created a tool for static analysis of hardware descriptions, which can derive certain information about an architecture automatically. The derived information can then be used for lifting the given concrete syntax of, for instance, instructions, to an abstract one.

## 1.3 Outline

The rest of this thesis is structured as follows. Chapter 2 presents preliminary work relevant for the topic of this thesis. Next, Chapter 3 discusses related work and certain requirements, from which we deduced the necessity of our research. A brief overview of the synthesis system that we created during that research is given in Chapter 4. Following, Chapters 5 to 7 detail the structure of the synthesis system, starting with the description of the input in a domain-specific language, and ending with a discussion of the generated code. Chapter 8 explains the abstraction techniques which we integrated into the synthesis system as an improvement. Next, two case study chapters first present the implementation of simulators using our new language (Chapter 9), and then illustrate how the generated simulators can be applied to microcontroller programs for the respective platforms (Chapter 10). Finally, Chapter 11 concludes this thesis.

## 1.4 Bibliographic Notes

Parts of the research presented in this thesis has been previously published in some of our earlier publications. The idea of retargeting a model checker by means of a hardware description was first described in our contribution to a doctoral symposium [26], and in a journal article [79]. A first operative version was presented in [29]. Improvements over the initial version, which introduced early versions of some abstraction techniques, were the topic of another publication [28]. This publication also included a first version of our implementation of an abstraction called *path reduction* (originally created by other authors). We contributed to enhancing this technique in another publication [10], the results of which were first obtained using one of our generated simulators, before backporting them to the simulator used in the publication.

Related work by other authors is presented in the individual chapters, either within the presentation where appropriate, or in a concluding section dedicated to related work.

# 2 Preliminaries

Within this chapter, we introduce the background that this thesis relies upon. The main tiers of our work are model checking, static analysis, and compiler construction. Model checking is a technology for verifying systems, and is used, in our setting, for verifying properties of microcontroller programs. Static analysis is a technique that can serve for various purposes. We use it in both for supporting the model checker and in a more classical setting, that is, in a compiler for processing the input.

The rest of this chapter is structured as follows. First of all, in Sect. 2.1, we define notations that are frequently used throughout the thesis. In Sect. 2.2, we explain Kripke structures, which we use to model systems. The next section then introduces temporal logics, with a focus on Computation Tree Logic (CTL). In Sect. 2.4, we introduce the concept of model checking, and illustrate how model checking combines the previously defined temporal logics and Kripke structures. An overview of static analysis is given in Sect. 2.5. Finally, an introduction into the [MC]SQUARE model checking tool concludes this chapter.

Our descriptions of Kripke structures, temporal logics, and model checking, are based on Clarke et al. [16], and on Baier and Katoen [9]. For static analysis, we refer to Nielson et al. [49]. The description of the [MC]SQUARE model checker is based on Schlich [68] and on our own contributions to this project.

## 2.1 Notations

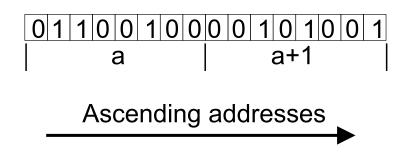

#### 2.1.1 Number Representations

For representing numbers by different bases, we abide by the notation used by Oberschelp and Vossen [51]. Hence, we define the following:

1. A number  $z \in \mathbb{N}$  is a short-hand representation of a sum:

$$z = (z_{n-1}z_{n-2}\dots z_0) = \sum_{i=0}^{n-1} z_i b^i$$

where  $n, z_i, b \in \mathbb{N}$ . *n* is the length of the representation and *b* is a base, also called a *radix* [78]. Unless specified otherwise, we use b = 10.

2. For representing a number by a base other than 10, we enclose the number by parentheses and append the value for b at the lower right parenthesis:

$(z)_b$

Hence, for instance  $10 = (10)_{10} = (1010)_2$ .

- 3. Hexadecimal values are prefixed with  $\partial x$ , for example  $\partial x f f$ .

- 4. Binary values are prefixed with 0b, for example 0b1011.

### 2.1.2 Fonts

Tool names are printed in uppercase, e.g. SGDL-STA. The names of temporal logics are printed in the same style, e.g. CTL. Java class names are printed in a slanted font, such as *Analyzer*. Finally, for code snippets we use a typewriter style, e.g. **execute**, and for longer code fragments we use a syntax highlighting appropriate for the respective language.

## 2.2 Kripke Structures

Kripke structures, or labeled transition systems, are a means for modeling concurrent systems.

### Definition 2.1. Kripke structure

Let AP be a set of atomic propositions. Let  $Pot(M) := 2^M$ , i.e., the powerset of M. A Kripke structure K over AP is defined as  $K = (S, S_0, R, L)$ , where

- S is a finite set of states

- $S_0 \subseteq S$  is the set of *initial* states

- Act is a set of actions

- $R \subseteq S \times Act \times S$  is a transition relation

- $L: S \to Pot(AP)$  is a function that maps each state to the set of atomic propositions valid in that state. L is also called *labeling function*.

This definition, which defines a set of actions that can be associated with transitions, is taken from Baier and Katoen. Actions are labels for transitions. The definition used by Clarke et al. does not require such a set, even though they sometimes also use labelled transitions.

Kripke structures extend the concept of propositional logics by states, which are also called universes. An *atomic proposition* no longer is either true or false,

```

1 r := initial node of the Kripke structure

2 visit(r)

3

4 visit(v)

5 for all successors v' of v

6 add v' to the tree

7 add edge (v,v')

8 visit(v')

```

Listing 2.1: Algorithm for unwinding a Kripke structure

but may have different values depending on the current state. Hence, using Kripke structures, it is possible to describe systems that evolve over time, such as automata, or programs modifying the memory of a computer device.

For reasoning about Kripke structures, we usually transform them into a tree representation, which is called a *computation tree* [16]. Computation trees are constructed by *unwinding* [16] the Kripke structure. We sketch the required algorithm in pseudo code in Listing 2.1. Note that the resulting tree may be infinite, as the Kripke structure may contain loops. Thus, the tree construction algorithm may not terminate. Each of the paths in the tree corresponds to a possible sequence of states in the Kripke structure. Such sequences are called *executions* by both Clarke et al. and Baier and Katoen.

## 2.3 Temporal Logics

Formulas in traditional propositional logics consist of Boolean statements called *atomic propositions*, and of conjunctions of such statements by means of operators such as AND, OR, and negation. Atomic propositions can be either true or false, but is possible to map more general expressions to these two truth values. For instance, it is legal to express that a variable v has a given value of 12 by an atomic proposition v = 12. The satisfiability problem for propositional logics (SAT) is decidable, though it is known to be NP-complete (Cook's theorem, as described in [3, 35]; a proof is given by Hopcroft et al. [34]).

A general assumption in propositional logics is that there is just a single universe, in which formulas can be evaluated to either true or false. This restriction complicates the modeling of time-related properties, e.g. specifying that a variable sequentially takes several given values. Kripke structures allow the modeling of such sequences, as each of the states can be seen as a certain point in time, and may have its own set of true and false atomic propositions. Furthermore, states in Kripke structures may also have more than one successor, corresponding to multi-

ple, possibly different, evolutions of a system. Properties that are satisfied on one set of paths need not necessarily be true on other sets. Hence, to benefit from these modeling possibilities, a logic should provide

- path quantifiers: a set of paths (e.g. all or at least one) satisfy a property

- recursion: conventional propositional and also predicate logic can only specify properties proportional in the length of the formula. In order to describe properties such as *eventually (after finitely many steps)* or *always*, it is necessary for the logic to provide a recursional description mechanism.

These restrictions are remedied by temporal logics. Two of these are LTL and CTL, which we describe in more detail in the following sections. Both are special cases of a more generalized logic called CTL<sup>\*</sup>, from which they can be derived by imposing certain restrictions on the usage of path quantors and temporal operators.

An important aspect of temporal logics is that the term *temporal* does not relate to a precise timing. These logics typically do not provide the means to describe properties such as *whenever* p holds, after two seconds q holds. Instead, the term temporal rather refers to a relative order of events (cf. [9]), meaning that is it possible to describe sequences of events while omitting the exact period of time elapsing between them.

#### **Definition 2.2.** Temporal operators

A temporal operator is one of  $\{X, F, G, U\}$  with the following semantics:

- $X\Phi$  means that the formula  $\Phi$  holds starting from the next state, seen from a current state s in a Kripke structure.

- $F\Phi$  means that the formula  $\Phi$  eventually holds.

- $G\Phi$  means that the formula  $\Phi$  holds globally, i.e., in all states.

- $\Phi U \Psi$  means that the formula  $\Phi$  holds in all states along the path until a state is reached in which  $\Psi$  holds, and there has to be such a state.

#### Definition 2.3. Path quantifiers

A path quantifier is one of  $\{A, E\}$  with the following semantics:

- $A\Phi$  means that the formula  $\Phi$  has to hold on all paths starting from the current state.

- $E\Phi$  means that there has to be at least one path, starting from the current state, on which the formula  $\Phi$  holds.

## 2.3.1 LTL

Linear time temporal logics (LTL) allow formulas to express properties along paths of arbitrary length. The general assumption is that given a state s in a Kripke structure  $\mathcal{K}$  and a formula  $\Phi$ , there can be only one future of s, i.e. a sequence of successor states  $(s', s'', \ldots)$ . In case the unwinding of  $\mathcal{K}$  yields a tree containing nodes with multiple successors, the resulting paths are considered separately. All LTL formulas are implicitly preceded by an A path quantifier, hence

$\mathcal{K}, s \models \Phi \Leftrightarrow \Phi$  evaluates to true for each of the paths starting at s.

As the model checking tool [MC]SQUARE, which we used for our research, started as a CTL model checker without support for LTL, we conducted our research on the basis of the CTL model checking algorithm. At the time of this writing, the tool had recently been extended to additionally support LTL. Therefore, we do not provide further details on LTL, but only use this short reference to point out some of the characteristics of CTL in the next section.

### 2.3.2 CTL

Computation Tree Logic (CTL) is a branching time temporal logic. CTL can be derived from CTL\* by requiring that each path quantor must be combined with exactly one temporal operator and vice versa.

#### Definition 2.4. Syntax of CTL

Let AP be a set of atomic propositions. The set of CTL formulas over AP is defined as follows:

- p is a CTL formula  $\forall p \in AP$

- If  $\Phi$  is a CTL formula, then  $\neg \Phi$  is a formula

- If  $\Phi$  is a CTL formula, then

- $-AG\Phi, AF\Phi, AX\Phi$

- $EG\Phi, EF\Phi, EX\Phi$

are CTL formulas, where A and E are path quantors, and G, F, X are temporal operators, as declared above

• If  $\Phi, \Psi$  are CTL formulas, then

$-A(\Phi U\Psi)$

$- E(\Phi U \Psi)$

are CTL formulas, where A, E are path quantors and U is a temporal operator

- If  $\Phi, \Psi$  are CTL formulas, then

- $-\Phi \lor \Psi$

- $-\Phi\wedge\Psi$

- $\Phi \rightarrow \Psi$

are CTL formulas

Additionally, there is a *release* operator R, but that operator can be expressed by means of the other operators (cf. Clarke). Clarke also describes how to represent any CTL formula using only an existential subset, that is, using formulas containing only the operator and quantifier types EX, EG, and EU.

Unlike LTL, which specifies properties over single paths of the unwinding tree and implicitly requires these to be true for all such paths, CTL specifies properties over different paths starting from specific nodes in the tree. There is no implicit A quantifier.

### Example 2.1. Examples for CTL formulas

- $AG \neg (\Phi \land \Psi)$  : on all paths,  $\Phi$  and  $\Psi$  are mutually exclusive

- $EF\Phi$ : there is a path on which  $\Phi$  eventually holds

- $A(r_1 = 10 U r_{17} \ge 20)$  : on all paths, the atomic  $r_1 = 10$  must evaluate to true (i.e.,  $r_1$  has a certain value) until  $r_{17}$  is larger or equal to 20

## 2.4 Model Checking

Model checking is a formal method for verifying systems. Starting from a model of a system and a specification, a model checking algorithm can automatically verify whether the system satisfies its specification. In case the system is found to violate the specification, it is usually possible to create a counterexample, that is, a trace of events leading to the state of the system in which the specification is no longer satisfied. The procedure as such requires large amounts of memory, and it is possible that the model checking algorithm has to abort verification. In that case, it is possible that the result is only valid for the subset of system states visited so far, or that there is no result at all.

The underlying idea of model checking is that of exhaustive exploration of all reachable system states. It is possible to separate two phases, *exploration*, also called state space building, and *verification*, though some model checkers entwine these with each other, for instance in an alternating mode of operation that allows for early pruning of certain paths. In the state space building phase, the algorithm uses a given a set of initial states of the system, and checks this set for possible evolutions. All steps the system may take are examined, leading to a new set of states. These are then the basis for further exploration, and are again checked for possible evolutions. Eventually, when no more new states are created, state space building terminates, and the actual verification phase starts. In this phase, depending on the (means of) specification, the model checking algorithm typically searches the state space for patterns of states, such as chains on which all states satisfy some property. Finally, depending on the result of the verification phase, the aforementioned counterexample may be generated.

The following parts of this section focus on the use of Kripke structures and temporal logics in the context of model checking.

### 2.4.1 Specification

Prior to any formal verification, it is necessary to capture the requirements for a given system in a sound manner that is amenable to algorithmic uses. Natural language is not suitable for this purpose, as it is usually too vague and ambiguous. Even the result of a proper requirements analysis (e.g. [74]) does not provide the mathematically rigorous description of system properties that is needed. Hence, the first step towards formal verification by means of model checking is to translate the natural-language specification into a formula in some temporal logic, and to represent that formula in the input format of the model checking tool of choice.

The temporal logic introduced in detail the last section, CTL, allows the description of evolutions of a system. In our setting, which is formal verification of embedded software, the atomics are statements about the memory contents of a microcontroller. Paths relate to the sequence of steps the microcontroller takes while executing a program, that is, a statement involving temporal operators specifies possible computations, while path quantors impose requirements such as *all possible computations starting from here* or *at least one computation starting from here* must satisfy a given requirement.

### 2.4.2 Modeling

Using Kripke structures, it is possible to describe a system that may take several possible states. For software verification, the set of initial states is equivalent to the state the machine has before execution of the program starts. Each instruction then correlates to at least one transition from one state to another. That is, an instruction *modifies* the system state. In the terms of a Kripke structure, the state reached after execution of an instruction is typically labelled differently: a different program or line counter, and a different set of atomic propositions. Hence, statements on the value of such atomics may also evaluate differently for different states.

#### 2 Preliminaries

Modeling systems can be handled either manually or automatically. For general purpose model checkers such as SMV [16], NuSMV [14], and UPPAAL [39], the input describes a set of automata, represented in the idiom understood by the tool. Such an approach has various advantages, but also a number of disadvantages. For one, it is possible to deliberately add or omit information about the behavior of the actual system, which helps counter the state explosion problem (cf. the next section and Chapt. 8). On the downside, this also means that the modeling has to be done manually, which may become difficult for very large or complex systems, or when the modeling step has to be done anew. The latter typically becomes necessary when model checking is successful, i.e., when an error is found, and the problem is fixed in the system under test. Then, the new system candidate has to be checked again, which requires a new or modified system model.

In the case of the already mentioned software model checking, the likelihood of such changes is very high, considering that modifying a program is simple. However, this is not necessarily a problem for model checking, as the changes of machine state associated with instructions in any programming or machine-level language are predictable, either from the language definition or the processor data sheet. Thus, it is possible to automate the modeling step for software.

Examples for tools that provide automatic modeling are JAVA PATHFINDER [33, 83] (Java source code and Java bytecode), MOONWALKER [1] (CIL bytecode of Microsoft .NET programs), CBMC [17] (ANSI C), and [MC]SQUARE [68] (microcontroller binary code). The internal approaches in these tools vary profoundly, as for instance later versions of JAVA PATHFINDER and [MC]SQUARE interpret machine code for building state spaces, whereas CBMC translates the source code of the program into a boolean formula and delegates the actual checking to a SAT solver.

#### 2.4.3 Verification

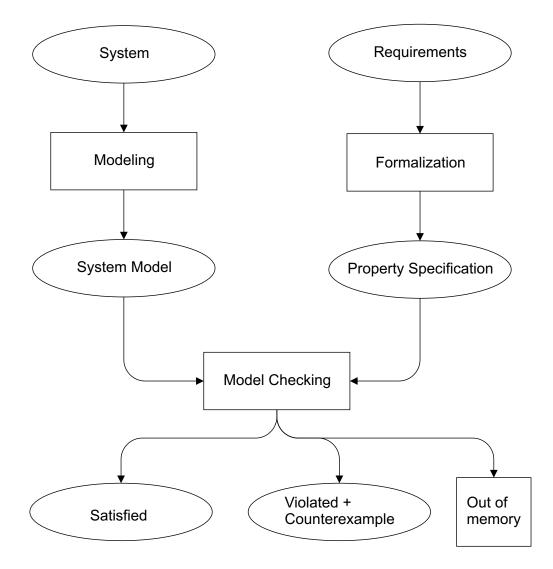

In the verification phase, the formalized specification and the system model serve as input for the model checking algorithm. Fig. 2.1 illustrates the procedure. Depending on the algorithm used, either a subset or the entire reachable state space is created and checked for property violations. Eventually, there may be three possible results. One of these is that the system model satisfies the formula, which means that no property violation was found. Another possible result represents the opposite case: some system state or a set of states violates the formula. In that case the model checker may attempt to create a counterexample (see below). Finally, the third possible situation is that the model checking algorithm was still active but ran out of memory, which resulted in a premature end of the verification. Such a situation may occur due to the state explosion problem, which refers to a rapid growth of the number of sytem states. This growth may be exponential in

Figure 2.1: Model checking procedure as described by Baier and Katoen [9] and Schlich [68]

the number of involved concurrent components in the system model, for instance the number of states of individual automata in an automaton-based system model.

Counterexamples illustrate the causes of errors, that is, property violations. They consist of a sequence of steps starting from an initial state, up to a state where a property from the specification no longer holds true. Hence, they provide an invaluable insight into problematic system behavior, which helps the developer reduce the number of remaining errors. This is fundamentally different from the outcome of testing, where only the effects of errors become visible, but not their origins.

Creating a counterexample is possible under certain circumstances, and its complexity depends highly on the logics used for specification. For automata-based LTL model checking [9], creating a counterexample imposes virtually no additional cost, as the necessary steps are part of the verification already. However, LTL verification is PSPACE-complete [9, 16], and therefore already very complex. On the other hand, CTL model checking does not automatically create a counterexample, which is why creating one requires additional effort. This is alleviated by the possibility to model check formulas with less time and space complexity than for LTL. Still, it is possible that some abstractions used during the verification process require special treatment of the state space created by the actual model checking algorithm in order to extract a counterexample from it, or that such a creation is altogether infeasible. One example for such an abstraction is path reduction (cf. Chapt. 8).

## 2.5 Static Analysis

Static analyses gather information about a program without actually executing it. Hence, the object of the analysis is not the binary program, as would be the case for dynamic approaches like testing. Instead, static analysis focuses on the source code. A variety of techniques exist, and some authors also include manual approaches such as code inspections, reviews, or code metrics (e.g. Liggesmeyer [40]). In this section, however, we do not consider these. Instead, we focus on automated techniques as described by Nielson et al. [49] and Aho et al. [2]. This section is based primarily on these two sources.

### 2.5.1 Motivation

Static analyses are extensively used in compilers, with the intention of optimizing a program at compile time. It is possible, for instance, to detect unnecessary and repeated computations, unreachable code, or loop-invariant code, i.e., code that could be moved out of a loop without altering the program semantics. Some examples for such uses are described below in this section.

Static analysis can also be used in stand-alone tools. Possible fields of application are vulnerability scanning [2] and the examination of timing behavior. For the latter and some additional examples, we refer to the section on related work in Chapter 6.

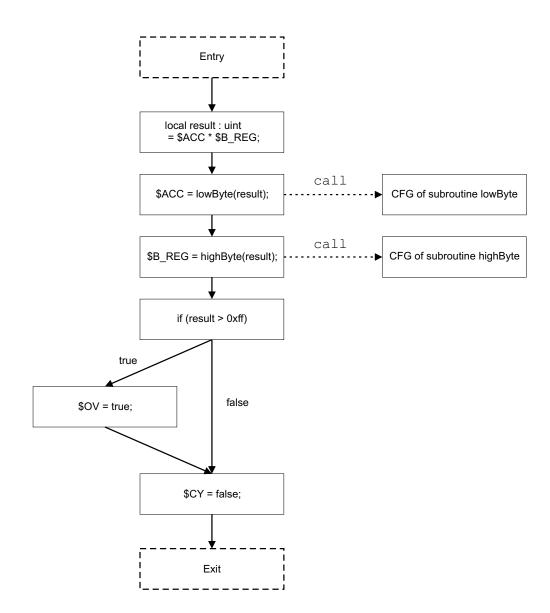

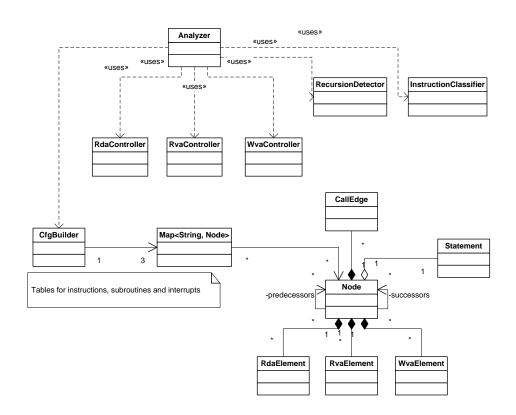

### 2.5.2 Control Flow Analysis

The goal of control flow analysis is to create a control flow graph (CFG) from a program. This graph illustrates the relation between instructions in the program, that is, possible successors, predecessors, loops and branches. Data flow analyses, which we describe below, typically operate on control flow graphs.

Creating the control flow graph can itself already be a challenging analysis. This is especially acute when analysing binary code. Under such circumstances, the successor relation is not always clear, for example due to the existence of indirect jumps. In some cases, like the analysis of potentially malicious code, the program may also be designed such that the control flow is not obvious.

### 2.5.3 Data Flow Analysis

As described by Nielson et al., data flow analyses can be conducted given

- a CFG, or flow relation

- a suitable lattice for representing the desired program properties

- a set of rules describing how program locations modify the analysis information

Then, it is possible to derive an equation system from the graph. The solution of the equation system can be obtained by a fixed point iteration.

Some examples of data flow analyses, and how they relate to specific optimizations in compiler construction, are listed below. These are taken from [2]:

- Live Variable Analysis: computes, for all program locations, the set of variables whose values are going to be read. Any variable not contained therein will either be overwritten before it is read the next time, or it will never be read again before the end of the program. Such variables are called dead. The corresponding code optimization employed by a compiler is called *Dead Code Elimination*: assignments to a dead variable can be removed from the program without altering the program semantics.

- Reaching Definitions Analysis: computes, for all program locations and all variables within scope, the locations at which these variables were last assigned a value (i.e., were defined). This analysis allows to determine potential values of variables at given program locations. In case a variable is found to have only a single possible value, it can be used by an optimization called *constant propagation*, which replaces variables by their known value.

• Available Expressions Analysis: computes the set of expressions that are certain to have been computed on the way to any program location. For an expression to remain in the set for a location, it must still evaluate to the same value, that is, no subexpression or variable contained therein may have changed. Using this analysis, it is possible to reuse previously computed expressions without computing their value again. The corresponding optimization is called *Common Subexpression Elimination*.

## 2.6 [mc]square

[MC]SQUARE is a model checker for microcontroller binary code, which was originally developed by Schlich [68] at the Embedded Software Laboratory of RWTH Aachen University in Germany. Over the years, several students of RWTH Aachen University as well as external partners contributed to it.

[MC]SQUARE operates on disassembled binary programs and follows a hardwaredependent approach: instead of providing a general purpose input language as an interface to the user, [MC]SQUARE can directly load the files intended to be deployed to the target microcontroller. Currently, it supports the Atmel ATmega16 and ATmega644, Intel MCS-51, and the Renesas R8C \23. Furthermore, it supports programs for Programable Logic Controllers (PLCs) written in Instruction List (IL) [84]. Previously supported platforms, for which support has been discontinued in [MC]SQUARE, comprise the Atmel ATmega128 and Infineon XC167. Concerning temporal logics used for specifying properties, [MC]SQUARE supports CTL. Formulas may contain atomic propositions about virtually any memory location occurring in a microcontroller, including registers and main memory.

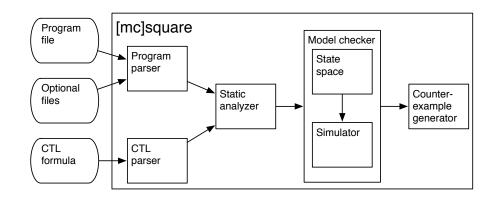

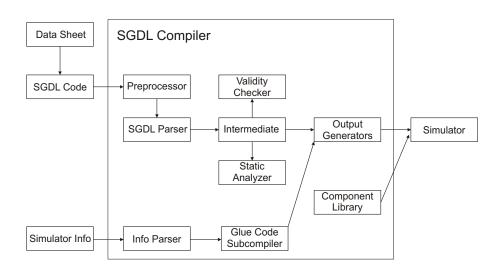

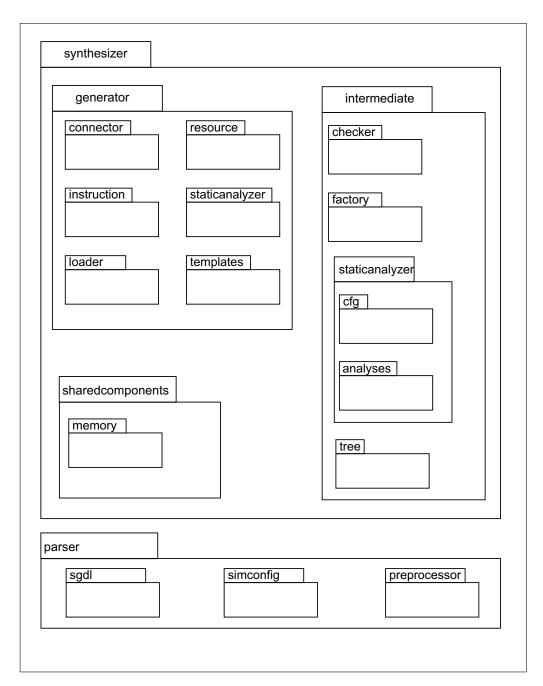

An overview of the model checking process implemented in [MC]SQUARE is shown in Fig. 2.2. Programs to be checked for property violations serve as the input to the tool, along with a formula. In a first processing step, both of these are parsed by suitable parsers and then passed to the core component of [MC]SQUARE, which consists of the actual model checking algorithm steering the verification, a simulator, and the state space. After termination of the model checking algorithm, and depending on the result, the counterexample generator may be triggered to extract a counterexample or a witness from the statespace created so far.

Programs are given as binary files in container formats such as ELF [80], Intel HEX, or Motorola S-Record. It is possible though not necessary to also provide the corresponding C source files, which, if present, can be used by [MC]SQUARE to create counterexamples that directly relate to source code lines. Otherwise, [MC]SQUARE is still able to point out problems with the input program, but will have to display errors in assembly only instead. In Fig. 2.2, the source code files are depicted as optional files.

Figure 2.2: Core components of the model checking process in [MC]SQUARE. The figure was originally designed by Schlich and since then used in most publications on [MC]SQUARE, including our own.

Both program and temporal formula may be preprocessed by a static analyzer. The task of this component is to discover useful pieces of information about the program and to annotate it accordingly. *Useful* in this context relates to possible reductions of the state space size during the actual model checking, for instance by determining when values are no longer required, or which parts of the program are entirely irrelevant for the result and can safely be omitted. We give an overview of the effects of these techniques and of related work in Chapter 8, Abstraction.

Simulators are used to create the state space in [MC]SQUARE. The tool provides a simulator for each of the supported platforms. At a glance, the mode of operation of these simulators resembles that of regular simulators, such as those provided by hardware vendors: they contain a model of the hardware, execute programs by applying the semantics of instructions to the aforementioned model, and simulate the effects of interrupts and on-chip peripheral devices. However, there are also several differences due to the requirements in state space building:

- Simulators in [MC]SQUARE need to support nondeterminism. Nondeterminism arises from the necessity of creating an over-approximation of the behavior of the real hardware, and is introduced into the system primarily from two sources: first, the assumption that the environment of the microcontroller may exhibit any behavior, and second, from interrupts, that may occur but may also not occur.

- Abstraction from time. The model checking algorithm used in [MC]SQUARE is based on the assumption that there is no time except for a partial ordering of events. This means that simulators do not have to keep track of the amount of time elapsed since a certain event, such as the start of the simulation, and

states accordingly do not have to store it. Hence, for states to be identical, it suffices that all memory locations are identical. This design decision in [MC]SQUARE eliminates the need for real time model checking algorithms, and also has the beneficial effect that states reachable in a loop may have to be stored only once. Therefore, the absence of time facilitates the verification process. A disadvantage, though, is that all timing-related on-chip peripherals also have to be considered to be able to show nondeterministic behavior. Therefore, timer and counter registers are also possible sources for nondeterminism.

- Third, the simulation should omit information irrelevant for the verification process. A very accurate simulation of internal processes of a device, such as the states of an analog to digital converter (A/D converter) may be help-ful when developing circuitry containing the actual device, but in the realm of model checking, this additional information may increase the number of different states that have be stored. Therefore, simulators in [MC]SQUARE do usually not simulate devices as accurately as the simulators provided by hardware manufacturers.

- Finally, the state of the hardware is frequently stored to and restored from the state space, requiring simulators in [MC]SQUARE to perform these two steps very quickly. This requirement excludes a complex object oriented internal data structure for state representations, as traversing such structures is very time-consuming. General purpose simulators from hardware vendors usually never have to perform save and restore steps, which is why they are not optimized for it, and consequently, perform poorly in this regard.

If desired, it is possible to provide a more accurate model of the environment in order to reduce the over-approximation of the behavior of external devices. Such a model is called a *user defined environment* (UDE), which we introduced in an earlier publication [70]. The UDE provides details about possible values of input ports and also internal devices such as timers, which are usually modeled using nondeterminism. UDEs are attached to the simulator component and extend it, without being visible to other parts of [MC]SQUARE. Without a UDE, model checking is still possible, as providing one is strictly optional.

The state creation process in [MC]SQUARE works as follows:

- Load a state from the state space into the simulator.

- Determine whether any nondeterministic bits need to be assigned a deterministic value, that is, either 0 or 1.

- For each assignment, decide whether it indicates the occurrence of an interrupt. If this is the case, then simulate the effect of that interrupt. Otherwise, proceed with the current instruction instead.

- Check atomic propositions for the state reached.

- Store resulting states in the state space. Add successor edges from the original state to the newly created ones.

Nondeterministic bits in the simulation represent either a 0 or a 1. Under certain circumstances, it is necessary to determine the actual value of such a location before simulation may proceed. A very frequent example of this is the decision whether a flag bit used by an active interrupt is set or not, that is, whether simulation has to continue in the way expected for *an interrupt occurred* or in the regular way. We call the process of determining the deterministic value, in compliance with Schlich [68], *instantiation* or *determinization*.

Instantiation of n nondeterministic bits results in  $2^n$  possible assignments, and consequently, states. Thus, the number of states increases exponentially in the number of instantiated bits, and consecutive instantiations typically result in state explosion. Therefore, several abstractions are implemented in [MC]SQUARE. Details on these are given in Chapter 8.

As pointed out before, [MC]SQUARE can create counterexamples and witnesses if necessary. These can be inspected on the GUI in different views: first of all, in either the assembly code or in the C code. In the presence of the source code and suitable debug information, these two panels are also linked, such that stepping through the states of the counterexample in one of the panels also updates the position in the other. Next, the counterexample can also be displayed graphically, as a sequence of states in the state space. Finally, it can be shown in the control flow graph on the static analyzer panel.

Apart from model checking, [MC]SQUARE also provides means for manual simulation. The developer may use the aforementioned C and assembly code panels to step through the program and inspect the reachable states. When interrupts are enabled, or nondeterministic choices on data occur, the simulator on the GUI allows to select a specific trace through the program. It is noteworthy that due to the state space being used for storing all seen states, this debugger also allows stepping backwards, which is a feature not normally found in software debuggers. In particular, this feature enables the developer to step backwards to points where choices were required (i.e., nondeterminism had to be resolved), and evaluate the effects of different choices.

# 3 Hardware Descriptions

The intention of this chapter is to point out the reasons for describing hardware, give an overview of available approaches, and establish the link to model checking of software for embedded systems. The latter step directly leads to a motivation of our research.

Several means for describing hardware were developed over the past decades, with different intentions. The most frequent reasons were either retargeting of existing tools, exploration of possible hardware designs, actually designing hardware, or simulating devices with the intention of developing software for these platforms. We provide an overview of these different goals in the next section. Section 3.2 contains a survey of existing approaches, which were designed to meet these goals.

In the third section, we point out why it is desirable to integrate a means for describing hardware into a model checker. Briefly, the issue encountered in the model checker [MC]SQUARE is its hardware-dependent approach. As [MC]SQUARE relies on simulators to build state spaces, it benefits from a very accurate model, and can provide exact and easy to understand counterxamples. On the downside, this approach renders it inherently hardware-dependent, and adapting it to new platforms is rather time-consuming. The requirements analysis in Section 3.3 therefore points out the features we deem necessary to remedy this hardware dependency.

## 3.1 Reasons for Describing Hardware

Within the scope of this section, we focus solely on the *reasons* for describing hardware designs by means of software. Examples for actual systems are given in the next section because many of these systems may be used for more than one area of application.

Hardware description languages can be classified in various ways. Some of them provide means for a low-level description of individual circuits and can be synthesized to actual hardware. The most prominent members of this class are VHDL and Verilog [42, 48], which can be used for designing devices and simulating their behavior on the level of signals. Other languages aim at the description of more specific classes of devices, such as processors. Unlike VHDL, these languages usually assume, for instance, that there are instructions to be processed by a device, with the consequence that there must be some means for loading, decoding, and executing them. Other typical assumptions may include the existence of special-purpose memory locations (registers), and among these, registers like a program counter and a stack pointer. For reasons pointed out below, we focus on processor-oriented languages.

Beyond this very coarse categorization, with VHDL / Verilog on one side, and special purpose languages for processors on the other, it is possible to create finer categories for the latter. A categorization which we consider helpful is presented by Halambi et. al. [32]. In their publication, they focus on systems on chip, and use the term *architecture description language (ADL)* for what we call processor-oriented. Their classification scheme is based on whether a language is designed primarily to describe the behavior of a device, or whether it rather focuses on describing its structure. Languages that allow, to some extent, to describe both, they call mixed level architecture description languages.

Another method of distinguishing languages is the level of abstraction they provide. VHDL provides a very low-level means of describing, based on state machines, clock cycles, and assignments to signals. Another level would be the *register transfer level*. On this level, actions performed by the hardware are described as assignments of values to individual registers. Machine instructions thus become a sequence of such assignments. Languages on this level are typically difficult to read and write. CSDL [59] is a language developed at the university of Virginia within the Zephyr compiler project. It consists of four languages, one of which is  $\lambda - RTL$ . This language is a register-transfer level language, but it already contains some improvements over plain RTL approaches for the convenience of a human developer. Contrasting to these low-level approaches, languages such as SystemC [42] resemble typical general-purpose programming languages.

#### 3.1.1 Tool Retargeting

The idea of avoiding reimplementation effort by means of high-level languages can be traced back at least to the advent of UNIX and the C programming language. According to Tanenbaum [77], from which this description of the history of UNIX and C is taken, the motivation for designing C was to be able to reimplement UNIX in a language that would ease porting the operating system to a new architecture. Instead of reimplementing the entire system, the necessary steps would be reduced to creating a C compiler that could generate code for the new architecture, and adapt some hardware-dependent parts written in assembler. Johnson eventually succeeded in creating such a portable C compiler. For details and references, we refer to the overview by Tanenbaum.

As C is still a relevant language in the operating systems and embedded systems domain, C compilers are still relevant as well. Therefore, it is necessary to create C compilers for new platforms. There are two approaches to this:

• retargetable C compilers

• generation of C compilers

An example for a retargetable C compiler is the GNU Compiler Collection, commonly referred to as GCC [24]. GCC has a backend that uses so-called machine description files, which are necessary for translating the intermediate code into binary code for the target machine. Supplying a new set of these files is therefore sufficient for adding support for a new platform to GCC. The other approach would be the generation of C compilers. Certain hardware description languages and associated toolkits facilitate the retargeting of C compilers, or even create entire tool chains consisting of compilers, assemblers, linkers, and profilers. Some of these are listed in the next section.

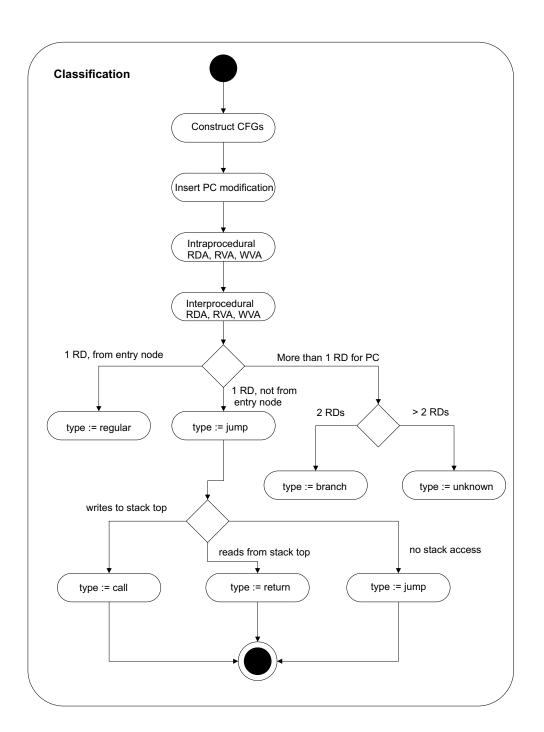

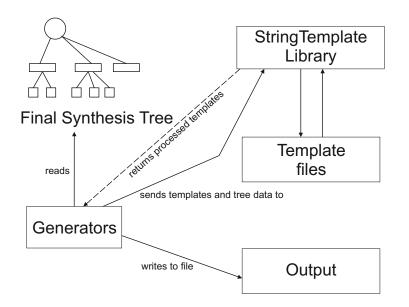

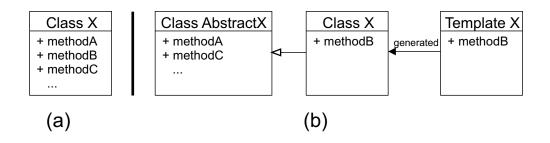

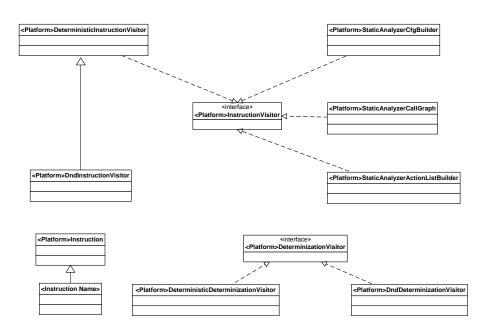

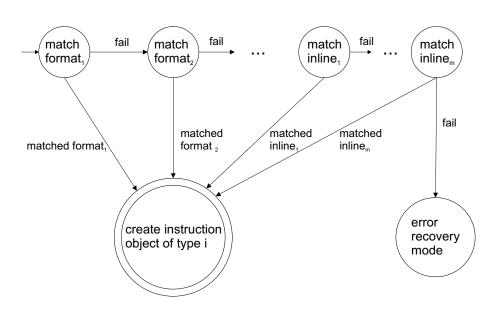

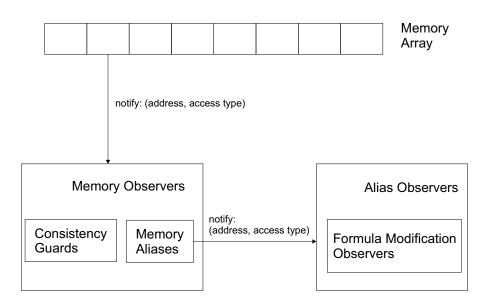

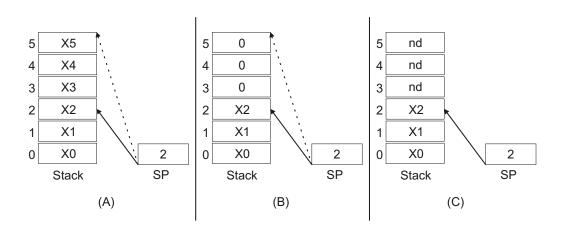

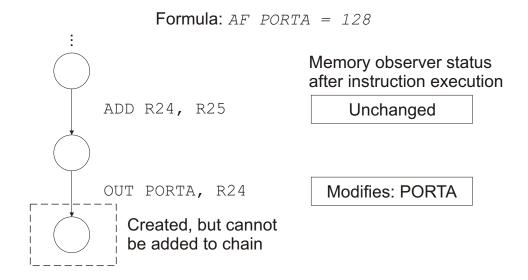

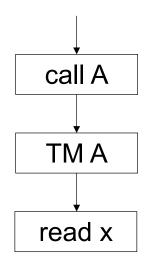

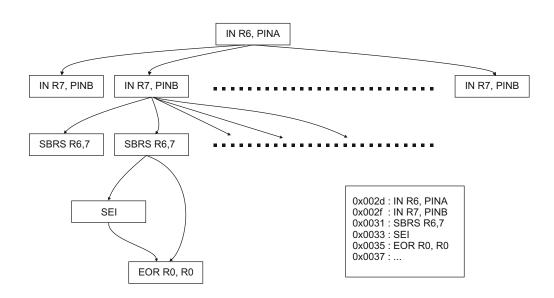

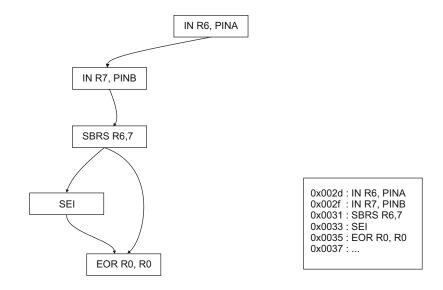

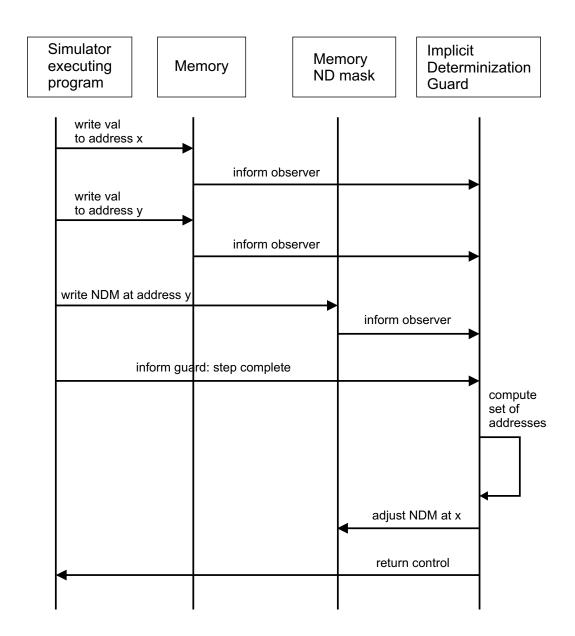

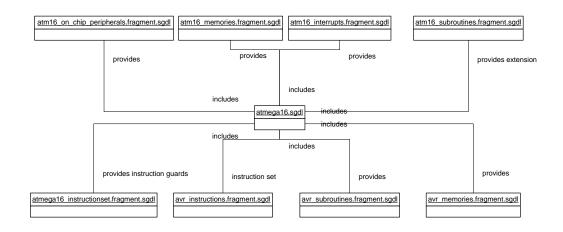

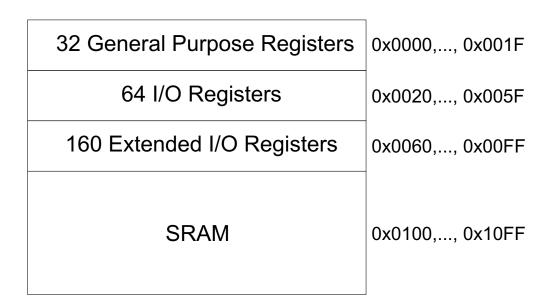

#### 3.1.2 Synthesis and Simulation of Actual Hardware